## 4-bit Binary Full Adder with Fast Carry

# HITACHI

#### Description

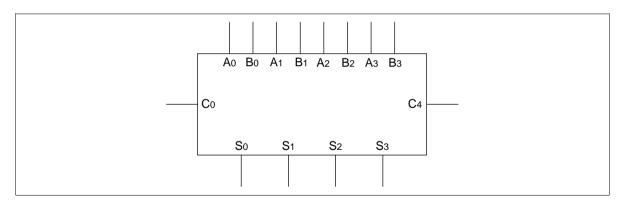

The HD74AC283/HD74ACT283 high-speed 4-bit binary full adder with internal carry lookahead accepts two 4-bit binary works  $(A_0 - A_3, B_0 - B_3)$  and a Carry input  $(C_0)$ . It generates the binary Sum outputs  $(S_0 - S_3)$  and the Carry output  $(C_4)$  from the most significant bit. The HD74AC283/HD74ACT283 will operate with either active High or active Low operands (positive or negative logic).

#### Features

- Outputs Source/Sink 24 mA

- HD74ACT283 has TTL-Cmpatible Inputs

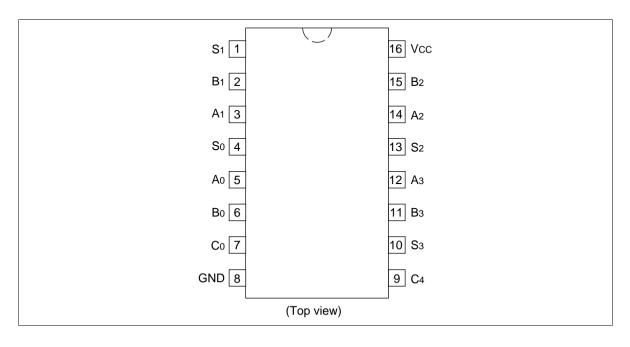

#### **Pin Arrangement**

#### Logic Symbol

#### **Pin Names**

$A_0 - A_3$  A Operand Inputs

$B_0 - B_3$  B Operand Inputs

C<sub>0</sub> Carry Input

$S_0 - S_3$  Sum Outputs

C<sub>4</sub> Carry Output

#### **Functional Description**

The HD74AC283/HD74ACT283 adds two 4-bit binary words (A plus B) plus the incoming Carry ( $C_0$ ). The binary sum appears on the Sum ( $S_0 - S_3$ ) and outgoing carry ( $C_4$ ) outputs. The binary weight of the various inputs and outputs is indicated by the subscript numbers, representing powers of two.

$2^{0} (A_{0} + B_{0} + C_{0}) + 2^{1} (A_{1} + B_{1}) + 2^{2} (A_{2} + B_{2}) + 2^{3} (A_{3} + B_{3}) = S_{0} + 2S_{1} + 4S_{2} + 8S_{3} + 16C_{4}$ Where (+) = plus

Interchanging inputs of equal weight does not affect the operation. Thus  $C_0$ ,  $A_0$ ,  $B_0$  can be arbitrarily assigned to pins 5, 6 and 7 for DIPS. Due to the symmetry of the binary add function, the HD74AC283/HD74ACT283 can be used either with all inputs and outputs active High (positive logic) or with all inputs and outputs active Low (negative logic). See Figure a. Note that if  $C_0$  is not used it must be tied Low for active High logic or tied High for active Low logic.

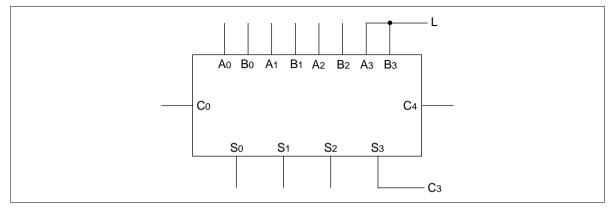

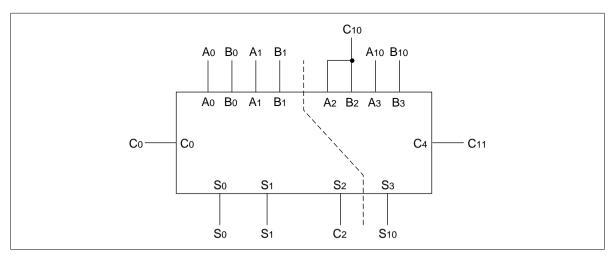

Due to pin limitations, the intermediate carries of the HD74AC283/HD74ACT283 are not brought out for use as inputs or outputs. However, other means can be used to effectively insert a carry into, or bring a carry out from, an intermediate stage. Figure b shows how to make a 3-bit adder. Tying the operand inputs of the fourth adder ( $A_3$ ,  $B_3$ ) Low makes  $S_3$  dependent only on, and equal to, the carry from the third adder. Using somewhat the same principle Figure c shows a way of dividing the HD74AC283/HD74ACT283 into a 2-bit and a 1-bit adder. The third stage adder ( $A_2$ ,  $B_2$ ,  $S_2$ ) is used merely as a means of getting a carry ( $C_{10}$ ) signal into the fourth stage (via  $A_2$  and  $B_2$ ) and bringing out the carry from the second stage on  $S_2$ . Note that as long as  $A_2$  and  $B_2$  are the same, whether High or Low, they do not influence  $S_2$ . Similarly, when  $A_2$  and  $B_2$  are the same the carry into the third stage does not influence the carry out of the third

#### HITACHI

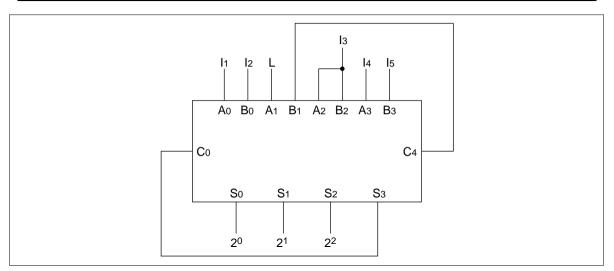

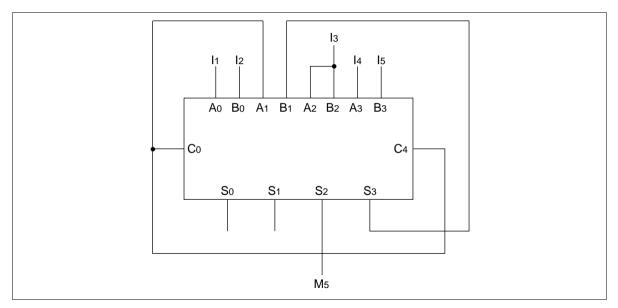

stage. Figure d shows a method of implementing a 5-input encoder, where the inputs are equally weighted. The outputs  $S_0$ ,  $S_1$  and  $S_2$  present a binary number equal to the number of inputs  $I_1 - I_5$  that are true. Figure e shows one method of implementing a 5-input majority gate. When three or more of the inputs  $I_1 - I_5$  are true, the output  $M_5$  is true.

#### Fig. a Active HIGH varsus Active LOW Interpretation

|              | C <sub>0</sub> | $A_0$ | $\mathbf{A}_{1}$ | $\mathbf{A}_{2}$ | $\mathbf{A}_{3}$ | B <sub>0</sub> | $\mathbf{B}_1$ | $B_2$ | $\mathbf{B}_3$ | S <sub>0</sub> | S <sub>1</sub> | S <sub>2</sub> | S₃ | $C_4$ |

|--------------|----------------|-------|------------------|------------------|------------------|----------------|----------------|-------|----------------|----------------|----------------|----------------|----|-------|

| Logic levels | L              | L     | Н                | L                | Н                | Н              | L              | L     | Н              | Н              | Н              | L              | L  | Н     |

| Active HIGH  | 0              | 0     | 1                | 0                | 1                | 1              | 0              | 0     | 1              | 1              | 1              | 0              | 0  | 1     |

| Active LOW   | 1              | 1     | 0                | 1                | 0                | 0              | 1              | 1     | 0              | 0              | 0              | 1              | 1  | 0     |

Active HIGH: 0 + 10 + 9 = 3 + 16

Active LOW: 1 + 5 + 6 = 12 + 0

Fig. b 3-bit Adder

Fig. c 2-bit and 1-bit adders

#### **HITACHI**

Fig. d 5-Input Encoder

Fig. e 5-Input Majority Gate

## Logic Diagram

Please note that this diagram is provided only for the understanding of logic operations and should not b used to estimate propagation delays.

#### DC Characteristics (unless otherwise specified)

| Item                                        | Symbol           | Max | Unit | Condition                                                                     |

|---------------------------------------------|------------------|-----|------|-------------------------------------------------------------------------------|

| Maximum quiescent supply current            | I <sub>cc</sub>  | 80  | μΑ   | $V_{IN} = V_{CC}$ or ground, $V_{CC} = 5.5 V$ ,<br>Ta = Worst case            |

| Maximum quiescent supply current            | I <sub>cc</sub>  | 8.0 | μA   | $V_{IN} = V_{CC}$ or ground, $V_{CC} = 5.5 \text{ V}$ ,<br>Ta = 25°C          |

| Maximum I <sub>cc</sub> /input (HD74ACT283) | I <sub>CCT</sub> | 1.5 | mA   | $V_{IN} = V_{CC} - 2.1 \text{ V}, V_{CC} = 5.5 \text{ V},$<br>Ta = Worst case |

#### **HITACHI**

## AC Characteristics: HD74AC283

|                         |                  | Ta = +25°C<br>C <sub>∟</sub> = 50 pF |     |      | Ta = –4<br>C <sub>∟</sub> = 50 |     |      |      |

|-------------------------|------------------|--------------------------------------|-----|------|--------------------------------|-----|------|------|

| ltem                    | Symbol           | V <sub>cc</sub> (V)* <sup>1</sup>    | Min | Тур  | Max                            | Min | Max  | Unit |

| Propagation delay       | t <sub>PLH</sub> | 3.3                                  | 1.0 | 11.5 | 15.0                           | 1.0 | 16.5 | ns   |

| $C_0$ to $S_n$          |                  | 5.0                                  | 1.0 | 9.5  | 11.5                           | 1.0 | 12.5 |      |

| Propagation delay       | t <sub>PHL</sub> | 3.3                                  | 1.0 | 10.5 | 14.0                           | 1.0 | 15.5 | ns   |

| $C_0$ to $S_n$          |                  | 5.0                                  | 1.0 | 8.5  | 10.5                           | 1.0 | 11.5 |      |

| Propagation delay       | t <sub>PLH</sub> | 3.3                                  | 1.0 | 14.0 | 17.0                           | 1.0 | 18.5 | ns   |

| $A_n$ or $B_n$ to $S_n$ |                  | 5.0                                  | 1.0 | 11.5 | 13.5                           | 1.0 | 14.5 |      |

| Propagation delay       | t <sub>PHL</sub> | 3.3                                  | 1.0 | 13.5 | 16.5                           | 1.0 | 18.0 | ns   |

| $A_n$ or $B_n$ to $S_n$ |                  | 5.0                                  | 1.0 | 11.0 | 13.0                           | 1.0 | 14.0 |      |

| Propagation delay       | t <sub>PLH</sub> | 3.3                                  | 1.0 | 9.5  | 12.5                           | 1.0 | 15.5 | ns   |

| $C_0$ to $C_4$          |                  | 5.0                                  | 1.0 | 7.5  | 9.5                            | 1.0 | 10.5 |      |

| Propagation delay       | t <sub>PHL</sub> | 3.3                                  | 1.0 | 10.0 | 13.0                           | 1.0 | 14.0 | ns   |

| $C_0$ to $C_4$          |                  | 5.0                                  | 1.0 | 8.0  | 10.0                           | 1.0 | 11.0 |      |

| Propagation delay       | t <sub>PLH</sub> | 3.3                                  | 1.0 | 11.5 | 14.5                           | 1.0 | 16.0 | ns   |

| $A_n$ or $B_n$ to $C_4$ |                  | 5.0                                  | 1.0 | 9.5  | 11.5                           | 1.0 | 12.5 | _    |

| Propagation delay       | t <sub>PHL</sub> | 3.3                                  | 1.0 | 12.0 | 15.0                           | 1.0 | 16.5 | ns   |

| $A_n$ or $B_n$ to $C_4$ |                  | 5.0                                  | 1.0 | 10.0 | 12.0                           | 1.0 | 13.0 | _    |

Note: 1. Voltage Range 3.3 is  $3.3 \text{ V} \pm 0.3 \text{ V}$ Voltage Range 5.0 is  $5.0 \text{ V} \pm 0.5 \text{ V}$

## AC Characteristics: HD74ACT283

|                                           |                  |                                   | Ta = +25°C<br>C <sub>∟</sub> = 50 pF |      |      | Ta = −40°C to +85°C<br>C <sub>L</sub> = 50 pF |      |      |

|-------------------------------------------|------------------|-----------------------------------|--------------------------------------|------|------|-----------------------------------------------|------|------|

| Item                                      | Symbol           | V <sub>cc</sub> (V)* <sup>1</sup> | Min                                  | Тур  | Max  | Min                                           | Max  | Unit |

| Propagation delay $C_0$ to $S_n$          | t <sub>PLH</sub> | 5.0                               | 1.0                                  | 11.5 | 13.5 | 1.0                                           | 14.5 | ns   |

| Propagation delay $C_0$ to $S_n$          | t <sub>PHL</sub> | 5.0                               | 1.0                                  | 10.0 | 12.0 | 1.0                                           | 13.0 | ns   |

| Propagation delay $A_n$ or $B_n$ to $S_n$ | t <sub>PLH</sub> | 5.0                               | 1.0                                  | 13.0 | 15.0 | 1.0                                           | 16.5 | ns   |

| Propagation delay $A_n$ or $B_n$ to $S_n$ | t <sub>PHL</sub> | 5.0                               | 1.0                                  | 12.0 | 14.0 | 1.0                                           | 15.5 | ns   |

| Propagation delay $C_0$ to $C_4$          | t <sub>PLH</sub> | 5.0                               | 1.0                                  | 9.0  | 11.0 | 1.0                                           | 12.0 | ns   |

| Propagation delay $C_0$ to $C_4$          | t <sub>PHL</sub> | 5.0                               | 1.0                                  | 10.0 | 12.0 | 1.0                                           | 13.0 | ns   |

| Propagation delay $A_n$ or $B_n$ to $C_4$ | t <sub>PLH</sub> | 5.0                               | 1.0                                  | 11.0 | 13.0 | 1.0                                           | 14.0 | ns   |

| Propagation delay $A_n$ or $B_n$ to $C_4$ | t <sub>PHL</sub> | 5.0                               | 1.0                                  | 11.5 | 13.5 | 1.0                                           | 14.5 | ns   |

Note: 1. Voltage Range 5.0 is  $5.0 \text{ V} \pm 0.5 \text{ V}$

### Capacitance

| ltem                          | Symbol          | Тур  | Unit | Condition        |

|-------------------------------|-----------------|------|------|------------------|

| Input capacitance             | C <sub>IN</sub> | 4.5  | pF   | $V_{cc} = 5.5 V$ |

| Power dissipation capacitance | $C_{PD}$        | 60.0 | pF   | $V_{cc} = 5.0 V$ |

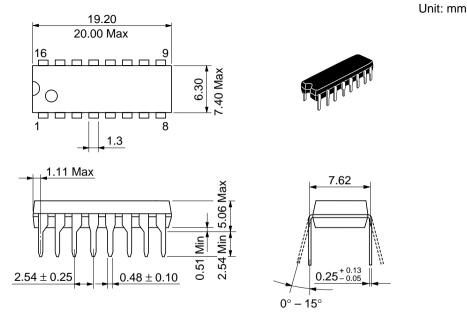

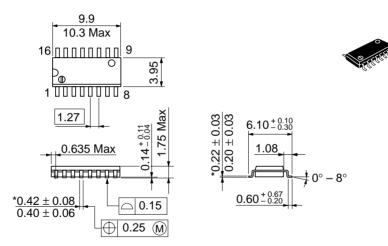

| Hitachi Code             | DP-16    |

|--------------------------|----------|

| JEDEC                    | Conforms |

| EIAJ                     | Conforms |

| Weight (reference value) | 1.07 g   |

Unit: mm

\*Dimension including the plating thickness Base material dimension

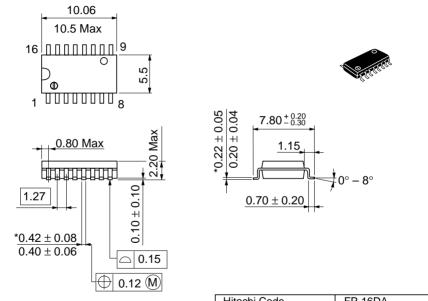

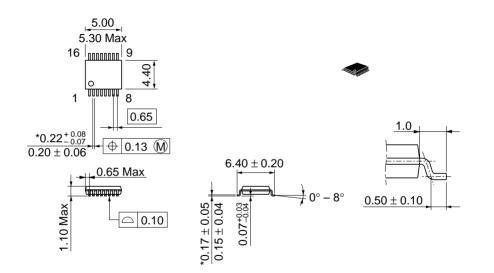

| Hitachi Code             | FP-16DA  |

|--------------------------|----------|

| JEDEC                    | _        |

| EIAJ                     | Conforms |

| Weight (reference value) | 0.24 g   |

Unit: mm

\*Dimension including the plating thickness Base material dimension

| Hitachi Code             | FP-16DN  |

|--------------------------|----------|

| JEDEC                    | Conforms |

| EIAJ                     | Conforms |

| Weight (reference value) | 0.15 g   |

Unit: mm

\*Dimension including the plating thickness Base material dimension

| Hitachi Code             | TTP-16DA |

|--------------------------|----------|

| JEDEC                    |          |

| EIAJ                     | _        |

| Weight (reference value) | 0.05 g   |

#### Cautions

- Hitachi neither warrants nor grants licenses of any rights of Hitachi's or any third party's patent, copyright, trademark, or other intellectual property rights for information contained in this document. Hitachi bears no responsibility for problems that may arise with third party's rights, including intellectual property rights, in connection with use of the information contained in this document.

- 2. Products and product specifications may be subject to change without notice. Confirm that you have received the latest product standards or specifications before final design, purchase or use.

- 3. Hitachi makes every attempt to ensure that its products are of high quality and reliability. However, contact Hitachi's sales office before using the product in an application that demands especially high quality and reliability or where its failure or malfunction may directly threaten human life or cause risk of bodily injury, such as aerospace, aeronautics, nuclear power, combustion control, transportation, traffic, safety equipment or medical equipment for life support.

- 4. Design your application so that the product is used within the ranges guaranteed by Hitachi particularly for maximum rating, operating supply voltage range, heat radiation characteristics, installation conditions and other characteristics. Hitachi bears no responsibility for failure or damage when used beyond the guaranteed ranges. Even within the guaranteed ranges, consider normally foreseeable failure rates or failure modes in semiconductor devices and employ systemic measures such as fail-safes, so that the equipment incorporating Hitachi product does not cause bodily injury, fire or other consequential damage due to operation of the Hitachi product.

- 5. This product is not designed to be radiation resistant.

- 6. No one is permitted to reproduce or duplicate, in any form, the whole or part of this document without written approval from Hitachi.

- 7. Contact Hitachi's sales office for any questions regarding this document or Hitachi semiconductor products.

Semiconductor & Integrated Circuits. Nippon Bldg., 2-6-2, Ohte-machi, Chiyoda-ku, Tokyo 100-0004, Japan Tel: Tokyo (03) 3270-2111 Fax: (03) 3270-5109 NorthAmerica URL http:semiconductor.hitachi.com/ http://www.hitachi-eu.com/hel/ecg Europe http://www.has.hitachi.com.sg/grp3/sicd/index.htm http://www.hitachi.com.tw/E/Product/SICD\_Frame.htm Asia (Singapore) Asia (Taiwan) Asia (HongKong) http://www.hitachi.com.hk/eng/bo/grp3/index.htm http://www.hitachi.co.jp/Sicd/indx.htm Japan For further information write to: Hitachi Semiconductor Hitachi Europe GmbH Hitachi Asia Pte. Ltd. (America) Inc. Electronic components Group 16 Collyer Quay #20-00 179 East Tasman Drive, Dornacher Stra§e 3 Hitachi Tower San Jose,CA 95134 D-85622 Feldkirchen, Munich Singapore 049318 Tel: <1> (408) 433-1990 Fax: <1>(408) 433-0223 Germany Tel: 535-2100 Tel: <49> (89) 9 9180-0 Fax: 535-1533 Fax: <49> (89) 9 29 30 00

Fax: <49> (89) 9 29 30 00 Hitachi Europe Ltd. Electronic Components Group. Whitebrook Park Lower Cookham Road Maidenhead Berkshire SL6 8YA, United Kingdom Tel: <44> (1628) 585000 Fax: <44> (1628) 778322

Hitachi Asia Ltd. Taipei Branch Office 3F, Hung Kuo Building. No.167, Tun-Hwa North Road, Taipei (105) Tel: <886> (2) 2718-3666 Fax: <886> (2) 2718-8180

Hitachi Asia (Hong Kong) Ltd. Group III (Electronic Components) 7/F., North Tower, World Finance Centre, Harbour City, Canton Road, Tsim Sha Tsui, Kowloon, Hong Kong Tel: <852> (2) 735 9218 Fax: <852> (2) 730 0281 Telex: 40815 HITEC HX

Copyright ' Hitachi, Ltd., 1999. All rights reserved. Printed in Japan.